AMD on the edge: Stripped down Siena Epycs teased

Hopes cool-running Zen cores can socket to Intel's Xeon-D – maybe with a smaller socket

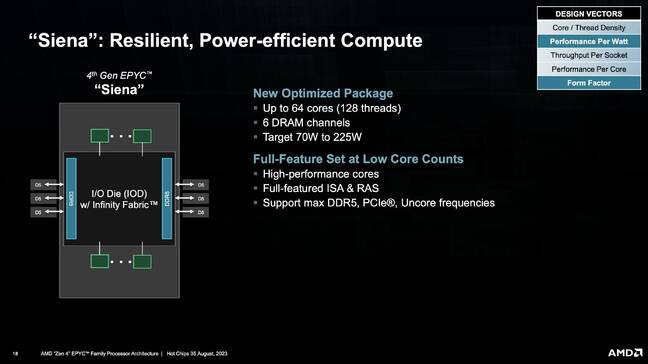

Hot Chips At the Hot Chips conference this week AMD teased its upcoming edge-friendly Siena family of Epyc processors, revealing modest power consumption and designs that allow them to nestle into relatively small devices.

As The Register reported in 2022, major server makers offer few AMD-based devices for the network edge, with Intel inside the majority of such devices because Chipzilla's Xeon-D range possesses many qualities that make it well-suited to, say, telco deployments.

Which is why the House of Zen this week showed off Siena processors that top out at 64 cores and offer just six memory channels. That's just half of what AMD offers in its Genoa or Bergamo platforms aimed at datacenters and clouds, but the biz feels edge operators won't miss that high-end power.

"The Siena platform here is targeted for performance per watt, and for a smaller and power efficient form factor," senior fellow design engineer at AMD Ravi Bhargava said at Hot Chips. "I say smaller, but it's still up to 64 of our high-performance cores with SMT 128 threads, the six DRAM channels all go up to [DDR5] 4800MT/sec, and, in general, you have all the features and capabilities, bells and whistles of all the other server products in Siena."

These trade-offs also mean Siena silicon will run at 70–225W – way less that its silicon siblings that can be configured up to 400W.

AMD hasn't revealed if Siena silicon uses its full-fat Zen 4 or the slimmer Zen 4c cores.

Bhargava's mention of "high-performance cores" might suggest the former – but in past remarks AMD used the similar terminology to describe its cloud optimized Bergamo processors, and they use Zen 4c cores.

AMD's telecom-optimized Epyc 4 Siena CPUs will offer up to 64 cores, six memory channels and a TDP of 70-225W … Click to enlarge

Slides shown at Hot Chips may offer some clues. The diagram depicting Siena appears to show a package with four-core complex dies (CCDs) surrounding the I/O die in the middle. Assuming the data the diagram depicts wasn't chosen to hold back some info before the chip's launch – a tactic AMD appears to have deployed in the past – the slides suggest AMD is using the same 16-core chiplets as Bergamo for Siena.

- Intel promises next year's Xeons will challenge AMD on memory, IO channels

- Need a datacenter processor? Try our take-and-bake Neoverse N2 cores, says Arm

- Nvidia just made a killing on AI – where is everyone else?

- Arm reveals just how vulnerable it is to trade war with China

Reusing CCDs in different products is one of the advantages AMD's chiplet architecture confers upon chip designers. For the silicon slingers upcoming MI300A APUs, it used the same 8-core Zen 4 dies that shipped on Genoa last northern Autumn. It would not be extraordinary for AMD to do something similar with Siena.

Another detail AMD did not mention is whether Siena will use a smaller socket than that required for Genoa and Bergamo processors. That possibility was raised early last year, when netizens spotted a diagram for an SP6 LGA socket that was much smaller than the massive SP5 socket introduced alongside Genoa.

A small socket certainly makes sense for the smaller devices that find their home at the network edge.

We won't have long to wait long to find out. Siena silicon is slated to ship later this year – and once it lands, AMD's Epyc 4 rollout will be complete. ®